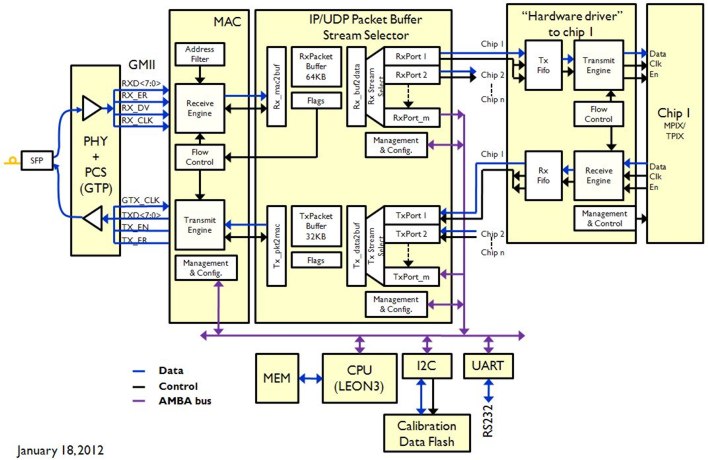

A general purpose readout system is

being designed to be able to readout Medipix / Timepix chips. A

Xilinx

Virtex-6 ML605 Evaluation board is used to test the functionality.

The ML605 board can be extended with an board that contains one or more

(maximum four) chips that need to be readout.

Currently the

Speedy

PIxel

DEtector

Readout module (SPIDR) is developed

to support up to 4 Medipix-3 chips.

The extension board is connected via the High Pin Count (HPC) FMC

connector on the ML605 board (J64)

A first goal is to readout four Medipix-3 chips mounted on a SPIDR

board, via 1000BASE-T (1 Gbit Ethernet electrical: RJ45) or 1000BASE-X

(1 Gbit Ethernet optical: SFP) using IP/UDP to transport the data. The

block diagram below gives an overview of the system:

A separate test design was made to test the MAC and the IP/UD buffers.

This design implements "n" FIFO-like channels that encode or decode UDP

(Jumbo) packets based on their UDP port number. Unrecognized packets

are forwarded unaltered to an "Others" channel that typically connected

to a CPU. The MAC implements flow control (Pause Request as defined in

IEEE802.3‐2008 Annex 31B).

Further documentation can be found here: "

GB

Ethernet UDP interface in FPGA".

Prliminary

documentation on SPIDR

can be found here.